本文档采用FPGA技术设计SDRAM控制器,分为四个主要模块:SDRAM控制器模块,控制接口模块,控制模块和数据传输模块。

SDRAM控制器模块调用其他三个模块并集成设计,为SDRAM提供同步控制接口和多个控制寄存器。以实现的功能是:SDRAM的初始化,SDRAM读写复杂定时的简化,定期生成更新命令。制器已成功模拟MAX plusII软件,仿真结果表明,由于控制器接口,SDRAM的操作非常简单。外,通过编程Verilog硬件描述语言实现的电路设计可以灵活地修改,大大增加了电路设计的多功能性和便携性。

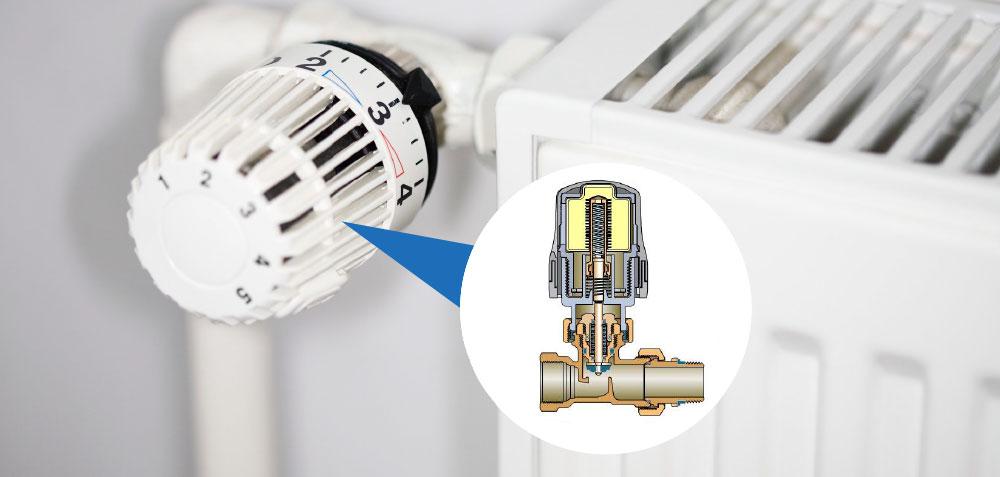

FPGA; SDRAM;控制器分类号:TP333文献代码:A文章编号:1671-7597(2013)041-024-02有关的信息的处理,特别是对于实时处理视频图像,有必要大量使用SDRAM。现了数据缓存,但SDRAM的复杂控制逻辑及其同步要求使得使用起来非常不方便。了方便用户使用SDRAM的,该文件提出了一个Verilog设计一个SDRAM控制器内核软件的基于FPGA的普遍使用,其中包括SDRAM几乎所有的模式,所以用户可以根据设备设置实现自己。用特定SDRAM的特定操作模式。入到SDRAM在这种设计中,恒温阀芯HYBANV4162020 4Banks×1M×16bit的力士被用作控制目标和它的工作时钟可以达到133 MHz,这是一种高速存储器。HY57V641620销被分为三类:控制信号:芯片选择(CS_N),同步时钟(CLK),有效的时钟(CKE),读/写(WE_N),有效数据(DQM)的选择等。地址信号:行地址选择(RAS_N),列地址选择(CAS_N),行/列地址行(SA0到SA12),时分复用,行行存储体块地址(BA0到BA1),数据信号:DQ0到DQ15,双向数据。被激活以由DQM控制。为一般规则,SDRAM将具有多个存储体。寻址时,首先通过BA的值确定存储体,然后在所选存储体中选择相应的行和列进行寻址。须先激活选通线信号。SDRAM启动后,必须先执行初始化,然后再执行其他操作。SDGA控制器FPGA设计本设计利用Altera的EP2C5-208 CyloneII FPGA芯片实现SDRAM控制器的设计。SDRAM控制器采用模块化设计,由四个主要模块组成:SDRAM控制器模块(上模块),控制接口模块,控制模块和数据传输模块。高级别的模块调用三个较低的模块并集成设计。制接口模块(连接到主机存储器地址)接收命令,解码命令,并将命令请求发送到控制模块。

制模块接收控制接口模块的命令和地址,并将适当的命令发送到SDRAM。据传输模块在写入和读取命令时控制数据传输。SDRAM控制器框图在图1中示出的模块控制器控制接口到主机控制接口模块进行解码,并记录命令并将该控制模块中的解码的命令。外,控制接口模块还包括SDRAM模式寄存器的设置,可以设置突发读/写长度和SDRAM预充电周期。始化SDRAM时,通过接口模块输入寄存器设置值。

制模块的控制模块接收已由控制接口模块解码的命令,从更新控制逻辑接收刷新请求,并在SDRAM中生成命令。模块包括一个仲裁器,用于仲裁来自刷新控制逻辑的主机接口命令和刷新请求。新刷新控制逻辑的请求具有比主机接口命令更高的优先级。果主机刷新命令和请求同时到达或者使用隐藏的刷新操作命令到达,则仲裁器将在响应命令之前等待隐藏的刷新操作完成主持人如果主机操作命令正在进行中,它将等待主机操作命令完成,然后才响应隐藏的刷新操作命令。旦裁判已经从主机接收到命令,该命令就被发送到控制模块的命令生成器部分。SDRAM发出的命令之间,控制模块通过三个可替换的寄存器进行定时。一替换寄存器用来控制ACTIVATE命令的定时,第二控制WRITEA和READA订单的结构中,第三记录顺序的持续时间,这允许仲裁,以确定是否最后的操作请求已经提出。

了。制模块执行SDRAM的多路复用地址命令。命令ACTIVATE(RAS)将线地址发送到SDRAM的引脚A [11:0]时,线地址输出有效。

地址的输出在READA(CAS)或WRITEA命令期间有效,该命令将列的地址返回给SDRAM。OE输出信号(由控制模块产生)用于控制数据传输模块的数据输入线末端的三态缓冲器。据传输模块数据传输模块在SDRAM和主机之间提供数据接口。行WRITEA命令时,主机数据通过DARAIN传输到SDRAM。出READA命令后,数据通过DATAOUT发送到主机。据输入行包含两段流水线,以正确组织数据以关联CMDACK和SDRAM发出的命令。

据输出线由两段流水线组成,用于在READA命令期间记录SDRAM数据。果DARAOUT和CMDACK一起工作良好,输出数据流水线的延迟可以减少到零。SDRAM控制器的仿真该设计的功能仿真在MAX plusII环境中进行。2显示了控制SDRAM进行写操作的SDRAM控制器的仿真。真结果表明,SDRAM控制器对每个操作都有正确的同步输出。论本设计采用自上而下的设计理念,选择FPGA和Verilog HDL语言,成功设计出简单通用的SDRAM控制器。用控制器具有各种播放,写入和突发模式。

实际应用中,可以选择基本的读,写和刷新操作以满足系统的需要。用SDRAM进行高容量和高速数据缓存具有相当大的优势,并且使用可编程外设来控制SDRAM提供了更大的灵活性。

本文转载自

恒温阀芯 https://www.wisdom-thermostats.com