本文档介绍了基于FPGA实现高容量数据存储的解决方案。程序分析了FLASH作业的特点,在FPGA平台上进行FLASH控制,实现了高速存储的效果。于对设计要求的遵守,本文介绍了FLASH控制器的最简单架构,它可以优化FPGA资源。成技术,FPGA和存储在这些电子信息快速发展的时代,数据存储有很多应用,因此存在各种各样的媒体存储方法和方法。合于大容量数据存储的基材包括SRAM,SDRAM和FLASH中常用的三个存储介质的性能比较示于表1中。以看出,FLASH是一种高集成度,低功耗能源,低价,无同步更新,能量损失,无数据丢失等它优于其他存储介质,以满足高容量,低功耗设计和简单的架构设计要求。们使用FLASH作为存储介质。FLASH中有两种类型的FLASH NAND和NOR FLASH:它能够在芯片中运行程序。动效率非常高。适用于存储容量较小的应用,可以直接传输到外部RAM中的NOR FLASH芯片。行。

NAND FLASH具有高密度存储单元,适用于存储大量数据,可实现数据存储的高密度存储,快速擦除和读写速度以及快速访问要求。本NAND闪存简介为此设计选择的FLASH有8个焊盘,每个焊盘包含4096个块,每个块包含64个页面,每个页面包含2048个字节的数据区域和64个字节的SPARE区域。个芯片共享同一组IO端口,但控制信号用于一组。制信号包括指令锁定使能信号(CLE),地址锁定使能信号(ALE),程序使能信号(WE),读(RE),芯片选择使能(CE)信号和FLASH。态反馈信号(RB),信号分布如下图所示。FLASH编程操作以页面为单位执行。制器首先发送编程操作80h的开始指令并同时验证指令锁定使能信号(CLE)。个信号同时控制FLASH以捕获第一条指令。后在使ALE有效的同时发送一个五字节地址,FLASH进入一个有效的页面地址,然后发送2048 n字节的数据进行存储,最后发送一个程序结束指令,FLASH开始自动编程,数据在FLASH中强化。到结束指令后,来自切片的RB信号返回FLASH状态,高电平表示READY(上一步结束),低电平表示BUSY(上一步运行) )当信号RB为高时。级别之后,您必须发送状态查询命令70h以读取IO0的状态。果该位为“1”,则前一操作成功。果为“0”,则操作失败。块是新生成的无效块。FLASH读操作也以页为单位完成,并且需要开始,地址和结束指令的组合来控制FLASH读数据的传输。FLASH擦除以块为单位完成。获FLASH命令的每个组合后,整个块被擦除为未使用的块,并且在擦除完成后,您必须读取状态。FLASH完成以确定是否产生坏块。用的FLASH操作说明如下表所示。

于FLASH制造过程,FLASH的每一位在不使用时都保持为“1”,8位以一个字节为单位组合。数据需要固化时,相应的位从“1”到“0”。了保存信息,擦除包括将块的所有位恢复为“1”。块变坏使用时,块的位信息保持其原始状态并且不能被修改。果重复编程故障块,则合并信息是错误消息。SPARE区域是用户可自由使用的区域,可用于写入数据信息,纠错码等。工厂离开工厂时,它指示块是否是每个块的主页的SPARE区域的前两个字节中的不正确的块而不是缺陷块(如果它不是一个问题) “FF”。了在使用之前找到坏块的分布,有必要遍历整个FLASH芯片以建立关于坏块的完整信息表。句话说,扫描整个FLASH芯片,在每个主页中读取2048和2049字节的数据,知道所有坏块的分布并建立坏块的信息表。些用户将使用第一个FLASH元素来处理坏块并将坏块信息表存储在块中。是,在数据存储过程中,每当您必须读取块中相应的错误块信息时,可以在判断之后执行操作,并且在生成后对块执行随机编程操作新的缺陷块。此,设计将坏块信息表的维护作业划分为CPU,CPU提供可用的非坏块地址,并在生成坏块时更新信息表。现最简单的FLASH架构涉及最小化FPGA占用的资源。此,有必要澄清FLASH控制器和CPU的任务划分,并确保两者之间的无缝互连。控制器提供给CPU和FLASH互连的外部接口如图n所示。CPU维护故障FLASH块信息表,以便根据故障块信息表将可用块地址提供给PLC;当控制器检测到产生新的故障块时,新的故障块地址被发送到CPU。块上的信息表由CPU更新。

时,CPU根据每个数据源的数据量和数据接收器的状态产生擦除和读取FLASH数据的指令。控制器接收到指令时,控制FLASH执行相应的操作。了确保可以正常存储不同数据速率的不同数据源,每个数据源将数据发送到控制器,控制器将数据存储在内部缓冲区中,该缓冲区以2048字节进行实例化。储该单元以便随后以页为单位将数据传输到FLASH。当从FLASH读取的数据也将在控制器中缓冲。

外部数据接收器准备好接收数据时,即。输出端,可以使数据存储和数据读取功能独立。数据接收器上读取数据时,还可以正常存储数据,从而提高控制器和FLASH的运行效率。

级模块的顶层模块主要用于控制和协调模块之间的工作,从每个数据源接收数据,并根据它们将它们发送到写操作模块的缓冲区。先级,与存储控制模块接口互连,并在收到指令后调度每个模块。行FLASH操作。控制状态机的工作流程如下图所示:上电后,控制初始化模块自动开始初始化,生成完整的BAT信息,然后等待。数据高速缓存已满或CPU发送命令时,将开始相应的操作。旦操作完成,就判断操作是否完成,即是否产生了错误的块。果生成了错误的块,则对错误的块执行相应的操作;如果没有生成错误的块,则操作返回到等待状态,等待下一条指令。者数据缓存已满。始化模块以页为单位遍历FLASH,分析每个页面的使用信息,并根据每个块的所有页面信息对块进行分类,以生成由CPU读取的BAT信息。

常使用。据分析,有8种类型的块,没有写入块,正常写入的完整块,正常的写入块但没有完整的块,不正确的写入块,块完全和替换,完整块替换但不是完整和初始不正确的块,其中初始坏块包括在先前初始化之前生成的工厂缺陷块和块。据每个块的类型,设计标记,并且诸如块中的逻辑块的数量,使用的页数等信息嵌入在BAT信息中并存储以等待CPU读取它们。FLASH写操作模块的写操作操作以页为单位,并且每次组合指令和地址时,命令FLASH执行页的写操作。操作如上图所示。

可以一次写入2048个字节的数据和64个字节的备用字节,也可以使用随机写入命令写入一个字节。了减少写操作的时间,设计将使用连续写操作指令和随机写操作指令同时写入2048字节的数据和品牌代码4个字节。操作模块主要负责控制FLASH以执行该操作。于FLASH的指令周期复杂且同步条件严格,因此需要选择适当的时钟周期来操作FLASH。操作模块发送FLASH指令和地址以控制FLASH的正常写操作。

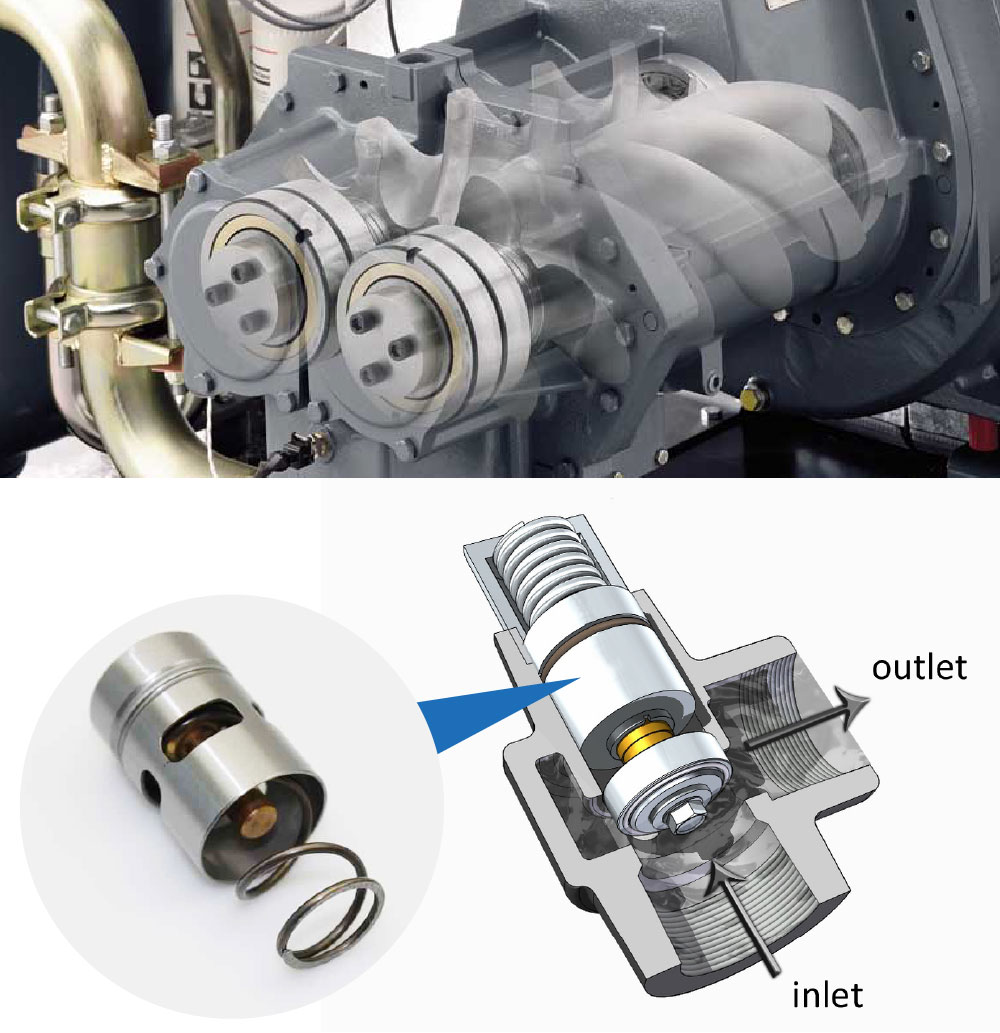

时,为了提高数据的写入速率,设计提出了用于写入数据的流水线操作,写入模块必须确保检查8个FLASH焊盘进行写入。道。旦每个写操作自动完成,恒温阀芯必须检查每个片以查看在写入页时是否生成了错误的块以及何时生成了错误的块,相同片的下一个块被检索为替换块,并从数据缓冲区调用write。新存储无效页面数据以确保数据完整性。FLASH读操作模块的读操作以页为单位读取。旦控制FLASH指令和地址组合控制FLASH,FLASH就自动加载数据。载数据后,信号RB变弱,然后为数据提供信号RE。

取,每次读取2048字节的数据。

块为单位执行擦除操作模块FLASH的擦除操作,并且每次组合指令和地址时,擦除FLASH并一次擦除一个块。旦擦除完成,RB信号变为低电平,控制器查询擦除操作以检查擦除操作是否完成并出现新的坏块。果生成了坏块,则会对其进行标记。签模块的主要功能是将写操作失败所产生的坏块和擦除操作失败标记为初始坏块,以便BAT表在下一次初始化时生成完成。

真和综合通过仿真工具和卡级测试进行验证,包括处理器和数据源,验证数据存储速率高达50 Mbps,数据读取速率高达10 Mbits / s,自动跳过坏块当使用新的坏块时,可以及时更新坏块信息表。300万个FPGA资源端口中只有9%,这是简化FPGA控制器并将资源留给其他所需设备的好方法。〔部分〕

本文转载自

恒温阀芯 https://www.wisdom-thermostats.com